[HFR] Actu : GTC: GPU: Maxwell puis Volta et DRAM stacking

Actu : GTC: GPU: Maxwell puis Volta et DRAM stacking [HFR] - HFR - Hardware

Marsh Posté le 19-03-2013 à 20:53:18 1

Le die stacking, C'est pas une nouvelle techno, c'est juste un peu cher, et peu employé dans les applications courantes.

Et le seul soucis, reste je pense dans ce cas précis thermique. C'est bien plus dur de faire de la dissipation thermique avec ce genre de techno ...

Encore que si c'est comme montré sur la photo, c'est du MCM et c'est la ram qui est stacké, ce qui reste assez "simple" à réaliser.

Perso j'attends les MCM qui remplaceront les multi GPUs, je pense ça ferra un bon de perf plus intéressant. Du burst sur la mémoire vidéo, c'est bien, mais c'est pas tout. Encore faut-il pouvoir traiter toute cette bouillie de pixels après.

Marsh Posté le 19-03-2013 à 21:05:31 0

Damien, Maxwell est-il confirmé en 20 nm, ou est-ce une supposition de ta part ?

Marsh Posté le 19-03-2013 à 21:11:33 1

Officiellement ce n'est pas confirmé mais ce n'est pas simplement une supposition de ma part.

Concernant le die stacking, Nvidia a bien précisé que ce serait mis en place avec des vias, il ne faut pas se fier trop à l'illustration.

Marsh Posté le 19-03-2013 à 21:28:10 0

| tridam a écrit : Officiellement ce n'est pas confirmé mais ce n'est pas simplement une supposition de ma part. |

OK, merci.

| tridam a écrit : |

Wow, des TSV sur une puce de ~200 W, ils n'ont pas froid aux yeux chez NVIDIA !

Marsh Posté le 19-03-2013 à 23:13:08 4

1. Petit lexique pour les non-initiés :

- MCM : sigle pour Multi-chip module

- VIA : "voie" en latin, ou rétro-acronyme pour Vertical Interconnect Access

- TSV : sigle pour Through-silicon via

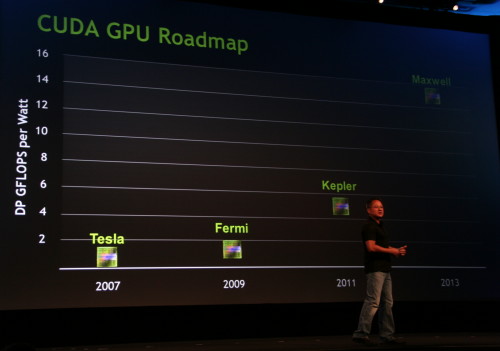

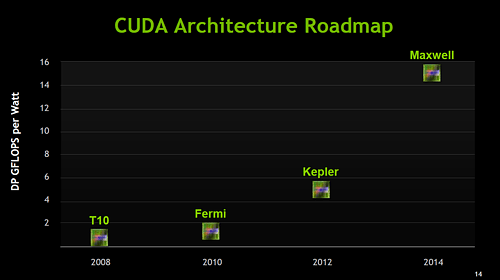

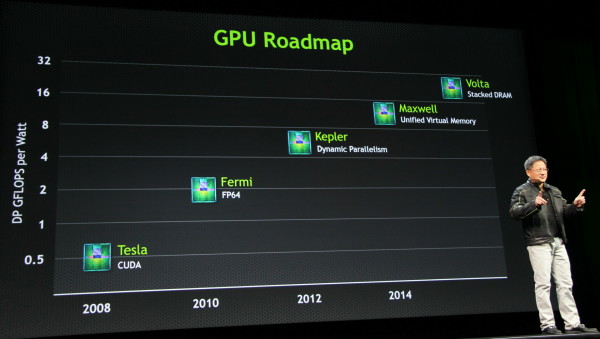

2. Jouons au jeu des sept erreurs avec Nvidia :

- Septembre 2010 (cf. ce focus) :

- Décembre 2012 (cf. cette news) :

- Mars 2013 (cf. ci-dessus) :

Après un petit décalage d'un an, Kepler passe de 5 à 6 Gflo/s/W en DP, et Maxwell de 15 à 12 Gflo/s/W DP... On table toujours sur une évolution exponentielle mais on tombe toujours sur du linéaire. ![]()

3. Boule de cristal :

Après les architectures NV40/NV47/G70 (130-110 nm en 2004-2005), G80 (90-80 nm en 2006-2007), Tesla (65-55 nm en 2008-2009), Fermi (40 nm en 2010-2011), Kepler (28 nm en 2012-2013), Maxwell (20 nm en 2014-2015), Volta (14nm en 2016-2017), aura-t-on enfin Ampère (10nm en 2018-2019) ?!

![[:greenwolf] [:greenwolf]](https://forum-images.hardware.fr/images/perso/greenwolf.gif)

Message édité par icorgnobi le 20-03-2013 à 02:08:03

---------------

Desktops et périphériques neufs en vente

Marsh Posté le 20-03-2013 à 01:16:39 1

L'illustration fournie ici par Nvidia ne semble pas du tout correspondre à l'explication faite du "die stacking".

Les prévisions exponentielles sur la puissance énergétique sont évidemment totalement farfelues et destinées aux investisseurs.

Kepler n'est pas trois fois plus performant que Fermi (deux fois), et les gains dus au HK gate-last et à la baisse fréquentielle, ne seront pas réitérables.

Marsh Posté le 20-03-2013 à 01:36:45 0

| regis183 a écrit : L'illustration fournie ici par Nvidia ne semble pas du tout correspondre à l'explication faite du "die stacking". |

L'illustration n'est rien autre qu'un montage grossier, il ne faut pas y chercher des détails.

Kepler triple par contre bien les Gflops/W en DP par rapport à Fermi, le graphe de Nvidia est plutôt proche de la réalité sur ce point. Pour les générations futures, cela reste bien entendu à prouver.

Marsh Posté le 20-03-2013 à 01:50:07 0

| tridam a écrit : Kepler triple par contre bien les Gflops/W en DP par rapport à Fermi |

Je me basais sur ça:

http://www.hardware.fr/articles/87 [...] -watt.html

edit: Ah ok, en DP

Message édité par regis183 le 20-03-2013 à 01:53:37

Marsh Posté le 20-03-2013 à 09:15:38 0

| Citation : +/- 24 Gflops/W pour Volta annoncé pour 2016 et 2017 |

faudrait peut etre qu ils se bougent un peu, j ai vu il y a deux semaines une demo d une puce tenant sur un PCB plus petit qu une carte Graphique et delivrant 80Gflop pour 400mW de conso et supportant OpenCL

Message édité par quicky2000 le 20-03-2013 à 09:19:39

Marsh Posté le 20-03-2013 à 09:58:42 0

| icorgnobi a écrit : |

Petite remarque sauf si je n'ai pas correctement interprété l'ironie, mais l’échelle de l'ordonnée qui est d'abord arithmétique sur les 2 premiers graphs devient géométrique sur le 3ème.

Marsh Posté le 20-03-2013 à 10:43:09 0

| tridam a écrit : Officiellement ce n'est pas confirmé mais ce n'est pas simplement une supposition de ma part. |

Mais des vias, elles pourraient être entre les dies de RAM empilés les uns sur les autres. Je n'ai pas encore regardé tout le discours de JHH certes ![]() mais je pense plutôt à des piles de RAM sur interposer qu'aller mettre ça sur le GPU, avec 200 watts dessous.. ça fait bien plus de puissance thermique au cm² que mes plaques de cuisson.

mais je pense plutôt à des piles de RAM sur interposer qu'aller mettre ça sur le GPU, avec 200 watts dessous.. ça fait bien plus de puissance thermique au cm² que mes plaques de cuisson.

D'ailleurs voici ce qui avait été publié au sujet de "Echelon", ou autrement dit Einstein, le successeur de Volta, on peut voir un GPU qui intègre un contrôleur mémoire et en dehors des "DRAM cubes"

Message édité par blazkowicz le 20-03-2013 à 10:46:31

Marsh Posté le 20-03-2013 à 10:53:44 0

quicky2000 a écrit :

|

powerVR ?

Marsh Posté le 20-03-2013 à 11:15:36 0

| ulukai08 a écrit : |

Une architecture "embarquee" mais pas du powerVR que je sache.

J attends de voir une annonce officielle pour avoir plus de details

Marsh Posté le 20-03-2013 à 13:32:39 0

Des monstres de puissance dans des labos, j'en ai connu en 25 ans... Ce n'est pas pour autant que ça donne quelque chose d'exploitable quelques années après.

Et surtout, sans vouloir te casser le moral, les FLOPS sont juste des opération en virgule flottante, qui peuvent être en simple précision (32 bits) ou double précision (64 bits). 80 GFlops ne veulent donc rien dire de concret sans donner la précision. NVidia annonce ses produits en double précision (DP) pour CUDA.

Marsh Posté le 20-03-2013 à 13:38:26 0

quicky2000 a écrit :

|

Tu ne peux pas comparer les perf\W de 2 puces qui ciblent des power et des usages très différents. Par contre, plus comparable, chez nVidia les 80Gflops sont atteint par le GPU du Tegra 4i (qui est un SoC dont on ne connait pas encore le TDP).

Maximiser les Flops/W sur une puce de 200W qui sera également destinée aux jeux vidéo, c'est une toute autre histoire...

Message édité par Fouge le 20-03-2013 à 13:38:48

Sujets relatifs:

- [HFR] Actu : BIOS UEFI GOP chez Asus pour les GTX 680

- [HFR] Actu : GTC: CUDA s'ouvre officiellement à Python

- [HFR] Actu : GTC: Nvidia GPU Technology Conference 2013

- [HFR] Actu : Une GeForce GTX 650 Ti Boost en préparation ?

Marsh Posté le 19-03-2013 à 19:30:02 0

Jen-Hsun Huang a profité de la keynote d'ouverture de la GTC pour mettre à jour la roadmap GPU globale de Nvidia. Pour rappel, après la génération Kepler ...

Lire la suite ...

Message édité par tridam le 19-03-2013 à 20:35:59