[Topic Unique] Processeurs AMD Llano A4/A6/A8 (APU 32nm)

Processeurs AMD Llano A4/A6/A8 (APU 32nm) [Topic Unique] - Processeur - Hardware

Marsh Posté le 29-05-2010 à 13:19:31

Les versions mobiles

Les déclinaisons mobiles de Llano n'étant pas au centre de mes préoccupations, vous avez le droit de me sonner pour mettre à jour cette partie...

Bien que les performances des Llano desktop soient encore inconnues, AMD a laissé filtré quelques informations quant aux déclinaisons mobiles. ![]()

Ainsi donc, c'est sous 3DMark Vantage en mode Performance (1280*1024) qu'on été "testés" les APU. (on soupçonne que ce soit le score GPU uniquement)

- Vision 2011 "E2-based" / APU E-350 / HD 6310 : 620

- Vision 2011 "A4-based" / APU A4-3300M / HD 6480G: 1625

- Vision 2011 "A6-based" / APU A6-3410MX / HD 6520G : 1882

- Vision 2011 "A8-based" / APU A8-3510MX / HD 6620G : 2842

Les modèles laptop attendus :

Fake ? Prudence !

HFR a publié un petit article sur le lancement des Llano mobiles...

C'est par ici pour la source originale => LIEN

| Citation : Conclusion : |

-----------------------------------------------------------------------

-----------------------------------------------------------------------

Message édité par Zack38 le 05-10-2011 à 18:49:15

Marsh Posté le 29-05-2010 à 13:19:39

Contenu à venir

Message édité par Zack38 le 26-05-2011 à 23:49:26

Marsh Posté le 29-05-2010 à 13:27:40

Tu devrais aussi expliquer le but de cet APU (c'est le même que chez Intel, qui a commmencé à en parler dès 2005).

Parce que sinon ça va troller dans tous les sens. ![[:cosmoschtroumpf] [:cosmoschtroumpf]](https://forum-images.hardware.fr/images/perso/cosmoschtroumpf.gif)

Message édité par marllt2 le 29-05-2010 à 13:28:43

Marsh Posté le 29-05-2010 à 13:34:17

Son objectif ... ?

Ben, c'est une étape du projet Fusion, dont le but avoué est d'aboutir à une architecture qui réunit tous les avantages du CPU et du GPU . L'autre but de Llano, c'est évidemment de concurrencer Clarkdale ...

Je ne vois pas ce que tu veux dire, marllt2 . ![]()

Marsh Posté le 29-05-2010 à 13:35:43

Que le but d'AMD et d'Intel n'est pas juste de transférer l'IGP du chipset vers le CPU.

Quand Intel a leaké les 1ères specs des SNB, tout le monde a dit: " Ah mais c'est nul, il y a un IGP sur des CPU de gamer ![]() "

"

| Zack38 a écrit : Son objectif ... ? |

Je parle de ça:

http://www.hardware.fr/articles/55 [...] -2005.html

http://www.anandtech.com/show/2884

Message édité par marllt2 le 29-05-2010 à 14:17:41

Marsh Posté le 29-05-2010 à 13:42:36

Va falloir que tu me dises avec des mots, parce que je suis incapable de visionner ces images . ![]()

C'est un PC de taf ..

Marsh Posté le 29-05-2010 à 13:54:29

En gros: Intel et AMD ont le même objectif -> pondre des CPU capables de réaliser des tâches classiques et massivement parallèles.

La première image montre une évolution: dual core -> multi-cores -> multi-cores + "many core" -> multiplication des unités de traitement "many core".

La seconde montre une prévision qui sonne le glas du multi-cores mi-2011, mais aussi l'apparition d'une archi "many core" (Larrabee) début 2010...

Marsh Posté le 29-05-2010 à 16:55:20

tu dis que llano pourra à peine faire tourner de la bureautique, internet etc... mais qu'ils sont plus véloces que les clarckdale,

c'est la partie graphique qui sera faible ?

Message édité par Profil supprimé le 29-05-2010 à 16:55:30

Marsh Posté le 29-05-2010 à 17:01:53

La partie graphique de Llano sera normalement beaucoup plus puissante que la partie graphique de Clarkdale, en raison de l'expérience GPU d'ATi . On pourra donc peut-être faire tourner de vieux jeux (avec 400SP c'est largement possible, il suffit de regarder les perfs de la HD5670) .

J'ai effectivement mal formulé l'info, je vais arranger ça ![]()

Marsh Posté le 29-05-2010 à 21:24:33

Voltage de la puce : Entre 0.8 et 1.3V.

Nombre de transistors : ~1 milliard.

Taille d'un core sans le L2 : 9.69 mm² pour 35 millions de transistors.

Taille d'un core avec le L2 : 17.7mm² pour 110 millions de transistors.

Conso d'un core : entre 2.5 (Idle) et 25W (>3GHz).

La conso totale sera d'environ 125W, soit 4x25W, et 25W de plus pour l'IGP (fréquence plus basse que le reste).

Socket: 722-pin pour la version Desktop (plateforme Lynx), et 812-ball BGA pour la version portable.

Ce sera le 1er CPU d'AMD qui utilisera le 32nm, le HKMG, et la 2e version de la lithographie par immersion.

L'UVD 2 sera bien sûr de la partie, comme on le peut le voir sur cette image...

Et pour ceux qui se demandent comment AMD parviendra à partager les accès mémoire entre le CPU et l'IGP, voici un début d'explication...

| Citation : Although the APU’s scalar x86 cores and SIMD engines share a common path to system memory, AMD’s first generation implementations divide that memory into regions managed by the operating system running on the x86 cores and other regions managed by software running on the SIMD engines. AMD provides high speed block transfer engines that move data between the x86 and SIMD memory partitions. Unlike transfers between an external frame buffer and system memory, these transfers never hit the system’s external bus. |

Modifications Llano vs archi K10.5 :

| Citation : The instruction window is enlarged to 84 entries so things should be a bit more efficient, and the instruction scheduler is now 30 entries for Integer, 36 for FP. Hardware integer divide is said to be improved and latency for FP instructions has been reduced as well. To fill these windows, there is a better prefetcher, cache lines transition between states faster, and memory fill speed is increased. The TLB is also improved for better residency. |

Il est probable que les premiers Llano fassent leur apparition dans des portables... et il est possible qu'ils aient une pomme comme logo.

Message édité par Wirmish le 29-05-2010 à 22:02:16

Marsh Posté le 29-05-2010 à 22:28:42

Je t'attendais, Wirmish ![]()

Mon plus grand contributeur ![]()

![]()

Par contre, la L2 prend tant de place que ça ? ![]() Il y a plus de transistors pour la mémoire cache que pour le core

Il y a plus de transistors pour la mémoire cache que pour le core ![]()

Marsh Posté le 29-05-2010 à 22:32:38

| Wirmish a écrit : Il est probable que les premiers Llano fassent leur apparition dans des portables... et il est possible qu'ils aient une pomme comme logo. |

Netbook ?

Style Atom ?

Marsh Posté le 29-05-2010 à 22:36:02

Tu connais beaucoup de marque dont le logo est une pomme ?

Moi, je dirais Apple, sans hésiter ![]()

Marsh Posté le 30-05-2010 à 00:39:02

| Logicsystem360 a écrit : Netbook ? |

Macbook, style "on veut pas de Core i, ça nous obligerait à utiliser 3 puces".

Une source pour les packages sinon? Car c'est pas très logique tout ça, à moins que Llano ne soit pas équipé de contrôleur PCI-E et son cousin à base de bobcat si...

Message édité par Gigathlon le 30-05-2010 à 00:41:23

Marsh Posté le 30-05-2010 à 01:03:47

| Zack38 a écrit : Mon plus grand contributeur |

.gif)

| Zack38 a écrit : Par contre, la L2 prend tant de place que ça ? |

Thuban (Phenom II X6) : 346 mm² (904 millions de transistors)

Deneb (Phenom II X4) : 258 mm² (758 millions de transistors)

Propus (Athlon II X4) : 169 mm² (300 millions de transistors)

Regor (Athlon II x2) : 117 mm² (234 millions de transistors)

Deneb (Phenom II X4) vs Propus (Athlon II X4) = 758 - 300 = 458 millions de transistors pour 6 Mo de cache.

À capacité égale, l'espace occupé par le L2 est exactement le même que pour le L3.

Et on peut constater que le cache L3 de 6 Mo du Deneb occupe ~33% du die, mais accapare 60% des transistors.

Et le ratio sera encore bien pire pour le cache L1 du Bulldozer...

Message édité par Wirmish le 30-05-2010 à 01:32:45

Marsh Posté le 30-05-2010 à 01:10:35

ReplyMarsh Posté le 30-05-2010 à 01:30:16

| Gigathlon a écrit : Une source pour les packages sinon? Car c'est pas très logique tout ça, à moins que Llano ne soit pas équipé de contrôleur PCI-E et son cousin à base de bobcat si... |

Le Llano et le Bobcat n'auront qu'un southbridge.

Je pense donc que le chip intégrera le northbridge.

EDIT: C'est bien ce que j'avais compris.

Le northbridge est intégré au die.

| Citation : Many of these improvements stem from AMD’s ability to fit the CPU cores, GPU cores and North Bridge (the part of the chip where the memory controller and PCI-express interfaces reside) onto a single piece of silicon. As noted earlier, this eliminates a chip-to-chip linkage that adds latency to memory operations and consumes power. It takes less energy to move electrons across a chip than to move those same electrons between two chips, and the power saved by this small change alone can help significantly increase system battery life. The co-location of all key elements on one chip also allows AMD to take a holistic approach to power management on these APUs. They can power various parts of the chip up and down depending on workloads, squeezing out a few milliwatts here and another few milliwatts there – which in the aggregate can amount to significant power savings. |

Message édité par Wirmish le 30-05-2010 à 01:35:05

Marsh Posté le 30-05-2010 à 01:32:04

ReplyMarsh Posté le 30-05-2010 à 01:37:25

| Wirmish a écrit : Mais qui a parlé du Regor ? |

Toi, tu t'es juste plantouillé.

Y'a pas de L1 doublé, juste le L2 de Regor qui passe à 2x1Mo, Propos étant en 4x512ko comme Deneb.

Marsh Posté le 30-05-2010 à 09:58:35

| Wirmish a écrit : http://forum.pwfrance.com/images/s [...] shy(2).gif |

En effet, la mémoire cache requiert énormément de transistors ... ! ![]()

| Wirmish a écrit : Le Llano et le Bobcat n'auront qu'un southbridge.

|

![[:dream49] [:dream49]](https://forum-images.hardware.fr/images/perso/dream49.gif)

Doit-on conclure que Llano, en plus de concentrer un CPU et un GPU au sein de la même puce, devra également compter un contrôleur-mémoire DDR3 plus un contrôleur PCIe ? Euh, le GPU risque de ne plus avoir beaucoup de transistors, vu comme ça ...

Marsh Posté le 30-05-2010 à 12:28:25

C'est pas compliqué: 1 bit nécessite 6 transistors (ou 8 pour le L1D de ceux à venir).

1Mo de L2 nécessite donc 2^20*8*6 = 50M de transistors (57M si ECC).

35M pour le core, 50/57M pour le L2, reste 18/25M à répartir dans la gestion du cache.

Quant au contrôleur PCI-Express, sa taille est dérisoire, il suffit de regarder le RD580 à l'époque (39mm² pour 36 liens PCI-E et 1 lien HTT, 22M transistors en 110nm)

Message édité par Gigathlon le 30-05-2010 à 12:38:33

Marsh Posté le 30-05-2010 à 15:07:18

Il faut donc plus de transistors pour une mémoire cache plus rapide ? ![]()

Marsh Posté le 30-05-2010 à 15:58:04

(Téléportation du post original dans le topic Bulldozer. ![]() )

)

Texte de remplacement:

Quelques infos (sérieuses ?) sur le TDP du Llano :

| Citation : According to sources familiar with the matter, different versions of Llano processor will have thermal design power varying from 20W to 59W: high-end dual-core, triple-core and quad-core chips will have TDP between 35W and 59W; mainstream chips with two of four x86 cores will fit into 30W thermal envelope and low-power dual-core Llano chips will have 20W TDP. |

@Zack38: Dans la partie "2°) Le point technique" tu devrais indiquer que le nouveau chipset est connu sous le nom de code "Hudson".

| Citation : The Hudson-D and Hudson-M3 input/output controllers will support PCI Express graphics port, 16 USB ports, USB 3.0 support (Hudson M3 only), 6 Serial ATA ports with RAID support, 1Gb Ethernet, integrated video DAC, integrated clock-generator and so on. |

Message édité par Wirmish le 30-05-2010 à 16:13:45

Marsh Posté le 30-05-2010 à 16:08:01

Cela signifierait ainsi que les Bulldozer auront 12 core natifs, soit dit 6 modules à la fin de leur vie ? ![]()

Marsh Posté le 30-05-2010 à 16:23:11

A première vue, 6 modules ça peut se faire, mais à ce moment il y aura un problème de bande passante...

Marsh Posté le 30-05-2010 à 16:36:08

De toute façon, je ne pense pas qu'il y ait d'application qui exploite vraiment douze core, même en 2012 ... m'enfin, sait-on jamais . Si jamais cela devait arriver, je pense qu'AMD renouvellerait ses chipset pour éviter que la BP ne soit trop limitée .

@ Wirmish : Ok, je MàJ avec ces nouvelles données . ![]()

Marsh Posté le 30-05-2010 à 16:41:15

| Gigathlon a écrit : A première vue, 6 modules ça peut se faire, mais à ce moment il y aura un problème de bande passante... |

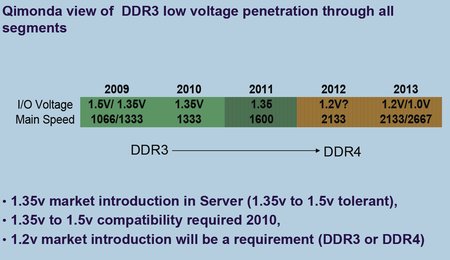

Ssi les proco utilisent toujours de la DDR3 en 2012 ... ![]()

EDIT: Une petite roadmap...

EDIT2: Dans ce brevet, déposé en juin 2008, Hynix parle même de DDR5 ! ![]()

Message édité par Wirmish le 30-05-2010 à 16:49:38

Marsh Posté le 30-05-2010 à 17:01:31

J'aimerais qu'on clarifie deux ou trois trucs à propos de Llano .

Premièrement, Llano n'aura normalement pas de mémoire cache L3 ?

Quelles informations a-t-on sur le Turbo de Llano ? Y'a longtemps, des infos ont circulé il me semble ... mais j'arrive plus à mettre la main dessus ![]()

Ensuite, à propos de la DDR4, c'est sûr que c'est prometteur, 1.2V pour 2133MHz ... ![]()

Marsh Posté le 30-05-2010 à 17:30:18

| Wirmish a écrit : EDIT2: Dans ce brevet, déposé en juin 2008, Hynix parle même de DDR5 ! |

C'est un gag ce brevet ou...?

10 pages pour déposer un brevet sur quelque chose qui découle du bon sens, c'est quand même un peu gros.

Pour ceux qui n'ont pas compris ce dont il était question, c'est la différence entre les figures 1 et 3 qu'il faut trouver, à savoir l'ordre des blocs passant de 0-1-2-3-4-5-6-7 à 0-4-1-5-2-6-3-7, dans le but de simplifier le routage. Y'a des gens qui font ça tous les jours sans déposer de brevet sur leurs routages, mais c'est pas grave.

Enfin ça n'apporte rien ici de toute façon, ils auraient même pu parler de DDR16 avec un prefetch de 65536, ça n'aurait pas rapproché la sortie de RAM de ce type.

Marsh Posté le 30-05-2010 à 18:16:27

Einh ? En quoi changer l'ordre des blocs améliore le routage ? S'ta dire ... ? Merci, quoi ! ![]()

Sujets relatifs:

- Vous preferez AMD ou INTEL ?

- [Topic Unique?] Asus Rampage III Gene [X58] [1366] [µATX]

- [Topic Unique] Coolermaster HAF X

- AMD BE-2350 ou Athlon X2 6000+ ?

- [conseil] AMD 6400+ vers INTEL Q9400 avec une 8800 GTX

- [Topic Unique] Silverstone HTPC Grandia GD06

- Carte mère pour Amd x2 250

![[:drap] [:drap]](https://forum-images.hardware.fr/images/perso/drap.gif)

Marsh Posté le 29-05-2010 à 13:19:15

.

![[:bakk10] [:bakk10]](https://forum-images.hardware.fr/images/perso/bakk10.gif)

Bienvenue sur le Topic AMD Llano !

Topic en chantier.

Merci de me MP pour vos questions/propositions d'ajout sur les premiers posts !

Avant de poster, veuillez prendre connaissance du règlement du forum !

Fiche récapitulative

Nom de code CPU : Llano

Nom de code Core : K12

Socket : FM1 (DDR3 @1866MHz)

IGP : Southern Islands, DX11 (HD5800, Vec5)

Finesse de gravure : 32nm SoI HKMG

Nombre de Cores : de 2 à 4

Fourchette de fréquences : 2.1GHz à 3.0GHz

Gamme de TDP : de 25W à 100W

Date de lancement : 30 Juin 2011

Fourchette de prix : de 64$ à 135$

Ce Topic traite majoritairement de la plateforme Lynx, c'est-à-dire de la plateforme Desktop de Llano. Les autres versions de l'APU seront traitées en second plan.

Contexte

Premiers fruits concrets du projet Fusion initié par AMD depuis le rachat d'ATi, les Llano rassemblent sur le même die un CPU et un IGP, le premier basé sur une µArchi K10.5 modifiée appelée K12, et le second tiré de la série Evergreen (Radeon HD 5000), le tout gravé avec une finesse de gravure de 32nm. Au final, ils constituent les premiers APU de la firme, terme marketing utilisé pour désigner les processeurs intégrant à la fois CPU et IGP. Leurs prix relativement attractifs, associés à leurs bonnes performances globales, en font un investissement très valable pour qui recherche un produit qui pourra lui fournir une puissance suffisante pour les applications quotidiennes et jouer occasionnellement, bien que ce ne soit clairement pas le créneau préféré des Llano.

Au niveau de leur positionnement dans la gamme, les Llano remplacent les Athlon II, et se placeront donc logiquement en face des Pentium et des Core i3 d'Intel. Ils remplaceront également en intégralité les CPU mobiles d'AMD.

En 2012, ils seront remplacés par les Trinity, qui changeront tout du tout au tout : changement de Socket (FM1 => FM2), de core (K12 => Piledriver), d'IGP (Southern Islands => Northern Islands).

Les topics en lien :

Les TESTS sont enfin sortis !!

En FRANÇAIS :

En ANGLAIS :

Les modèles

Les processeurs sortis

A8-3850 - 4C @2.9GHz / HD6550D (400ALU/20TMU/8ROP) @600MHz / 4x1Mo Cache L2 / DDR3-1866 / 100W / 135$ (30/06/11)

A8-3800 - 4C @2.4GHz (2.9GHz max) / HD6550D (400ALU/20TMU/8ROP) @600MHz / 4x1Mo Cache L2 / DDR3-1866 / 65W / 129$ (08/08/11)

A6-3650 - 4C @2.6GHz / HD6530D (320ALU/16TMU/8ROP) @433MHz / 4x1Mo Cache L2 / DDR3-1866 / 100W / 115$ (30/06/11)

A6-3600 - 4C @2.1GHz (2.4GHz max) / HD6530D (320ALU/16TMU/8ROP) @433MHz / 4x1Mo Cache L2 / DDR3-1866 / 100W / 109$ (08/08/11)

A6-3500 - 3C @2.1GHz (2.4GHz max) / HD6530D (320ALU/16TMU/8ROP) @433MHz / 3x1Mo Cache L2 / DDR3-1866 / 65W / 89$ (18/08/11)

A4-3400 - 2C @2.7GHz / HD6410D (160ALU/8TMU/4ROP) @600MHz / 2x512Ko Cache L2 / DDR3-1600 / 65W / 69$ (07/09/11)

A4-3300 - 2C @2.6GHz / HD6410D (160ALU/8TMU/4ROP) @433MHz / 2x512Ko Cache L2 / DDR3-1600 / 65W / 64$ (07/09/11)

Les processeurs qui sortiront prochainement

A8-3870K - 4C @3.0GHz / HD6550D (400ALU/20TMU/8ROP) @600MHz / 4x1Mo Cache L2 / DDR3-1866 / 100W / ???$ (T4 2011)

A8-3820 - 4C @2.5GHz / HD6550D (400ALU/20TMU/8ROP) @600MHz / 4x1Mo Cache L2 / DDR3-1866 / 65W / ???$ (T4 2011)

A6-3670 - 4C @2.7GHz / HD6530D (320ALU/16TMU/8ROP) @443MHz / 4x1Mo Cache L2 / DDR3-1866 / 65W / ??$ (T4 2011)

A6-3620 - 4C @2.2GHz / HD6530D (320ALU/16TMU/8ROP) @443MHz / 4x1Mo Cache L2 / DDR3-1866 / 65W / ??$ (T4 2011)

A4-3420 - 2C @2.8GHz / HD6410D (160ALU/8TMU/4ROP) @600MHz / 2x512Ko Cache L2 / DDR3-1600 / 65W / ??$ (T4 2011)

E2-3200 - 2C @2.4GHz / HD6370D (160ALU/8TMU/4ROP) @433MHz / 2x512Ko Cache L2 / DDR3-1600 / 65W / ??$ (T4 2011)

Athlon II X4 651 - 4C @3.0GHz / 4x1Mo Cache L2 / DDR3-1866 / 100W / 92$ (14/11/11)

Athlon II X4 631 - 4C @2.6GHz / 4x1Mo Cache L2 / DDR3-1866 / 100W / 72$ (15/08/11)

Note : en gras les processeurs avec la lettre suivante :

K : coeff libre

Le test !!!

Hardware.fr a testé séparément les deux parties de l'APU, d'abord le CPU et ensuite le GPU.

Tests du CPU

Tests du GPU

En 2012, Llano sera remplacé par Trinity. Au programme : des cores Star remplacés par

des modules Bulldozer, et une partie graphique boostée...

L'évolution des process chez GloFo, dans les années à venir...

Comparaison entre un die d'Athlon II X4 et un die d'A8 Llano...

Les chipsets

Message édité par Zack38 le 18-02-2012 à 23:07:38