[HFR] Actu : Intel et Micron annoncent 3D XPoint

Actu : Intel et Micron annoncent 3D XPoint [HFR] - HFR - Hardware

Marsh Posté le 28-07-2015 à 19:30:37 4

Dommage qu'il n'y ait pas plus de détail sur la techno.

Pour l'instant cela parait un peu magique. ![]()

Marsh Posté le 28-07-2015 à 20:07:04 3

Cela rejoint ce qui avait été évoqué dans cette news :

http://www.hardware.fr/news/14219/ [...] anaux.html

edit : Merci Guillaume pour cet article !

Message édité par Invite_Surprise le 28-07-2015 à 20:09:07

Marsh Posté le 28-07-2015 à 21:06:38 2

Petit slide Intel pas fait pour la presse, qui donne un (tout petit) complément d'infos : http://www.intelsalestraining.com/ [...] Pointc.pdf

Au conditionnel, "10x" la latence de la DRAM.

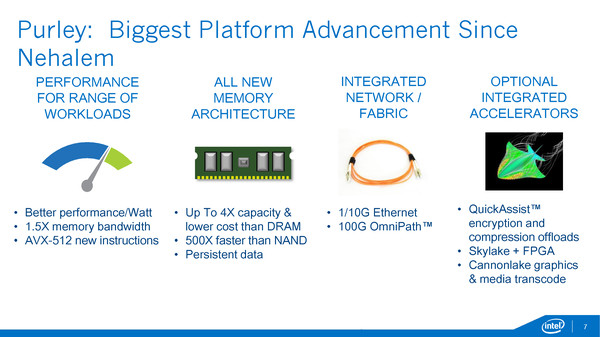

Je retiens le "Transforming memory hierarchy" qui va effectivement avec ce qui était sous entendu avec Purley, mais je me demande comment Intel va gérer ca en pratique. Il peut y avoir un intérêt a de la DRAM quand même sur la plateforme si il y a un ordre de magnitude entre XPoint et la DRAM (et au minimum pour la question de l'endurance). Donc soit proposer des plateformes avec au choix DDR4 et "DIMM XPoint", plus probablement un mix des deux, ou alors de (très) gros L4 "on package" pour faire l'intermédiaire. Tout dépend des performances réelles pratiques, il y a beaucoup d'endroit sur serveur ou sacrifier de la latence vs capacité est un excellent compromis (larges bases de données par exemple).

Et sinon tout en bas en petit, il est confirmé que c'est bien la latence qui est utilisée pour les comparaisons 1000x !

Marsh Posté le 28-07-2015 à 21:18:42 1

Curieux aussi de connaître le procédé du "changement des propriétés des matériaux", si c'est physique ou chimique.

Pourquoi pas des mini électrolyses ?

Marsh Posté le 28-07-2015 à 22:00:26 0

| TheRealBix a écrit : Curieux aussi de connaître le procédé du "changement des propriétés des matériaux", si c'est physique ou chimique. |

Perso je mettrais une petite pièce sur une variante de RRAM : https://en.wikipedia.org/wiki/Resis [...] ess_memory

Après si c'est bien ça, pourquoi ne pas l'avoir tout simplement dit ? La communication d'Intel ces dernières années est... particulière.

Marsh Posté le 28-07-2015 à 22:06:24 3

+1

Je viens de fouiller le net et effectivement, ça doit être basé sur de la RERAM ou quelque chose de similaire.

https://stacks.stanford.edu/file/dr [...] mented.pdf

Marsh Posté le 28-07-2015 à 22:24:14 1

| Gein a écrit : +1 |

Excellent PDF, merci !

Ca ressemble *très* fortement, intéressant de noter aussi la latence qu'ils atteignent avec leur prototype à 104ns (2eme schéma au dessus), soit un facteur de 10 par rapport à de la DRAM ![]()

Marsh Posté le 28-07-2015 à 22:51:04 0

De rien ![]()

Au moins, on a une idée un peu plus précise sur la techno (peut-être) employé ![]()

Marsh Posté le 29-07-2015 à 09:01:14 0

A voir si les chiffres avancés le seront en pratique compte tenu des marchés envisagés. Si c'est le cas ce serait enfin une avancé dans une période très creuse depuis plus de 10ans dans la recherche informatique, intéressant.

Marsh Posté le 29-07-2015 à 09:29:33 1

| Gein a écrit : |

Et donc : http://www.eetimes.com/document.asp?doc_id=1327289&

"The switching mechanism is via changes in resistance of the bulk material," was all Intel would add in response to questions sent via email.

Marsh Posté le 29-07-2015 à 10:01:34 1

PCPer indique concerne le procédé de fabrication :

| Citation : |

http://www.pcper.com/news/Storage/ [...] aster-NAND

Marsh Posté le 29-07-2015 à 10:10:51 0

Avec 4 layer ça doit être sympa au niveau de la densité ![]()

| C_Wiz a écrit : |

Hehe ![]()

Marsh Posté le 29-07-2015 à 10:21:30 0

ça sent la spintronique tout ça...

Mais de souvenir les nanopiliers étaient composés de 3 couches (et non 2) : 2 électrodes ferromagnétiques et une barrière pour les séparer.

L'état 0 ou 1 dépend du moment magnétique de chaque électrode, ie un état si les résultantes du moment magnétique des électrodes sont opposés, une autre si elles sont identiques.

Message édité par sanction le 29-07-2015 à 10:23:28

Marsh Posté le 29-07-2015 à 12:40:36 0

Intel a cependant parlé de l'intérêt de cette mémoire pour le jeu en général, laissant penser qu'il y aura des applications grand public.

perso ,je vois bien le cloud gaming mais pas sur le pc de mr tout le monde.

qui vivra verra

Marsh Posté le 29-07-2015 à 12:56:21 0

prochain bond en avant dans les SSD? ça fait envie tout ça ![]()

Marsh Posté le 29-07-2015 à 20:29:05 1

Je me permet de rajouter la structure extraite du même papier :

Je trouve que c'est bien plus explicite ![]()

Edit : And the magic is gone ![]()

Message édité par Gein le 29-07-2015 à 20:31:09

Marsh Posté le 30-07-2015 à 15:43:57 0

Cette disposition en interconnexion entre lignes et colonnes me fait penser au cablage interne d'un clavier. Il y a deja des soucis avec 108 touches...

Mais bon, rien d'insurmontable.

Marsh Posté le 30-07-2015 à 15:59:38 0

Ça peut être aussi de la MRAM (magnétique), comme le dit sanction.

En fonction de si les deux matériaux sont orientés magnétiquement ou pas, ça conduit (1) ou pas (0). C'est hyper rapide (meilleur que de la DRAM) et non volatile, et ça ne consomme quasi rien. Et surtout, beaucoup de monde travaille dessus. Ah et j'ai oublié : Les cellules ne s'abiment pas contrairement à la flash !!

Marsh Posté le 04-08-2015 à 14:22:33 0

Salamandar3500 : En parlant de consommation tu as une idée de l'ordre d'intensité qu'il faut pour retourner un spin ? A une époque, je me souviens de tests qui se faisaient entre 1mA et 100mA et je ne sais plus à quel voltage...

Sujets relatifs:

- [HFR] Actu : X99 en Micro-ATX chez Asus

- [HFR] Actu : Contrôleur NVMe x4 chez Phison

- config pr revit architecture 3D + multitasking (web/indesign) à 1000€

- Intel ou AMD pour un budget limité ?

- PC pour Gaming et application 3D (montage vidéo, etc...)

- Intel I7 4790k température

- différence entre un processeur AMD et Intel

- [HFR] Actu : Metal Gear Solid V en bundle Nvidia

Marsh Posté le 28-07-2015 à 19:20:02 1

Intel et Micron viennent d'annoncer conjointement une nouvelle technologie de mémoire baptisée « 3D XPoint » (à prononcer « 3D Crosspoint »). Les deux sociétés ...

Lire la suite ...